MCS-51, Interrupt Control System

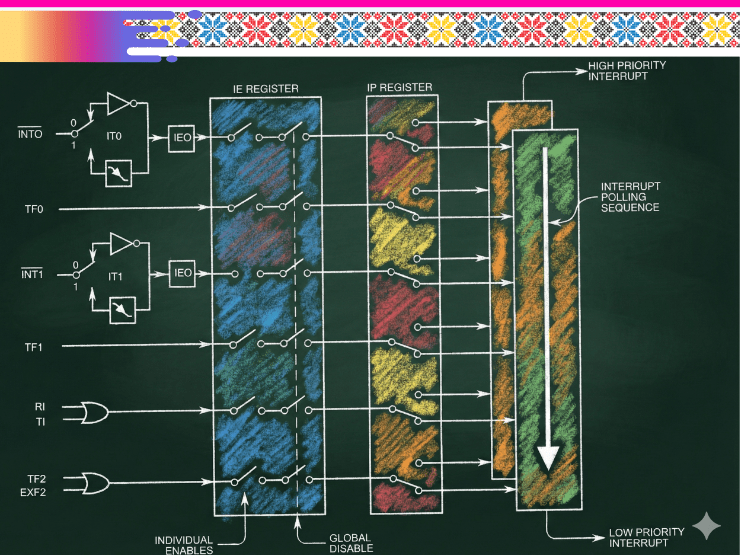

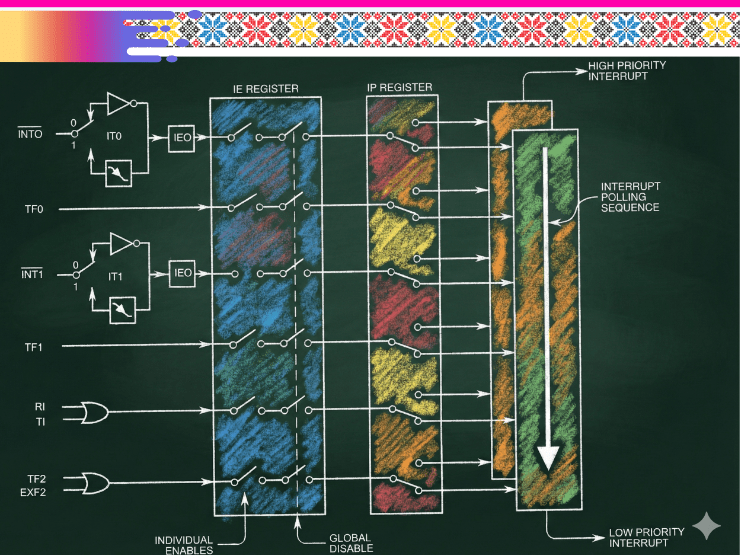

โครงสร้างของระบบการ Interrupt ของ MCS-51 เมื่อเกิดมีการอินเตอร์รัปสัญญาณต่างๆ ขึ้น จะส่งผลให้มีการควบคุมเพื่อสั่งให้โปรเซสเซอร์กระโดดไปทำงานที่ตำแหน่งแอดเดรสต่างๆ

โครงสร้างของระบบการ Interrupt ของ MCS-51 เมื่อเกิดมีการอินเตอร์รัปสัญญาณต่างๆ ขึ้น จะส่งผลให้มีการควบคุมเพื่อสั่งให้โปรเซสเซอร์กระโดดไปทำงานที่ตำแหน่งแอดเดรสต่างๆ

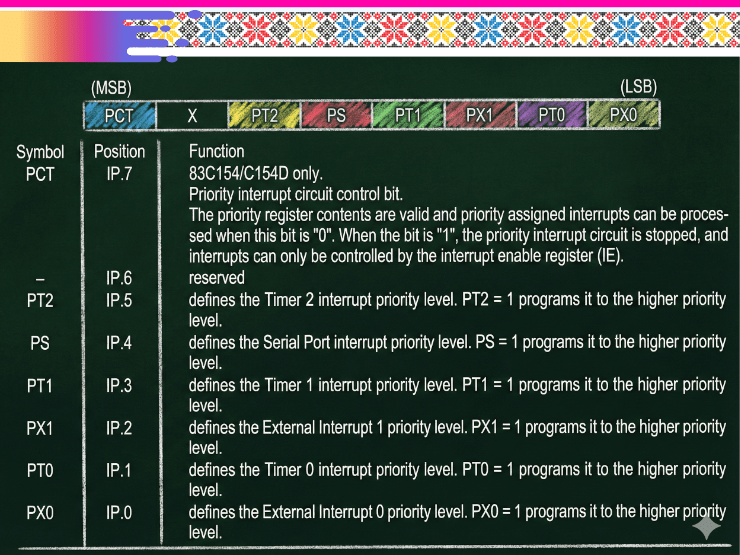

การกำหนดระดับความสำคัญให้กับสัญญาณ Interrupt สามารถทำได้โดยการกำหนดบิตข้อมูลใน IP

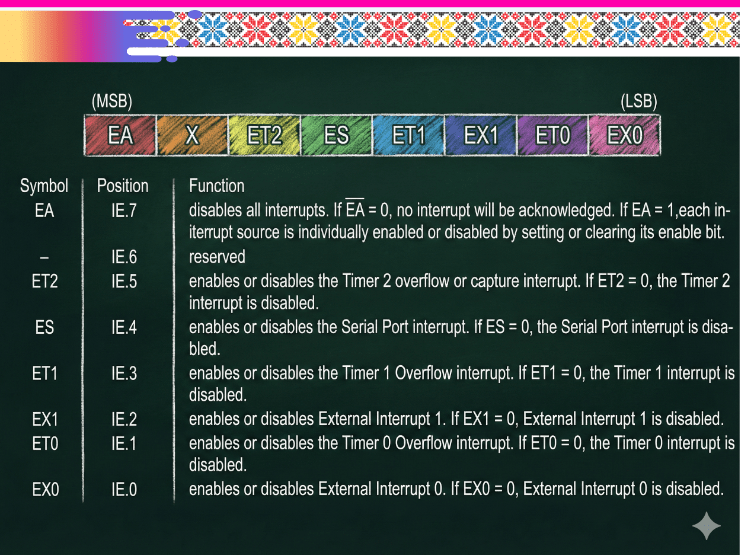

การจัดการ Interrupt ของ MCS-51 สามารถกำหนดเลือก Enable/Disable ให้มีการ Interrupt ของแต่ละสัญญาณได้ โดยใช้วิธีการกำหนดค่าของ Bit ภายใน Register IE

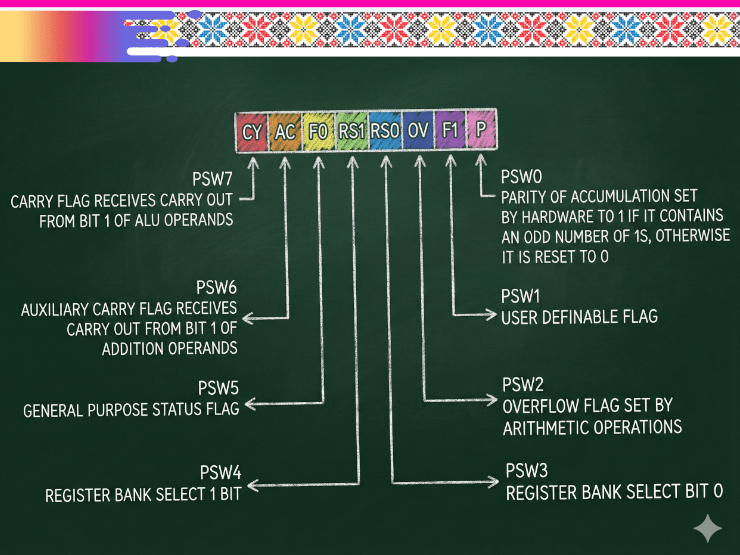

Register ซึ่งทำหน้าที่บอกถึง Flag แสดงสถาวะการทำงานต่างๆ รวมทั้งบิตสำหรับการกำหนดเลือก Blank ของ Register ที่ใช้งาน

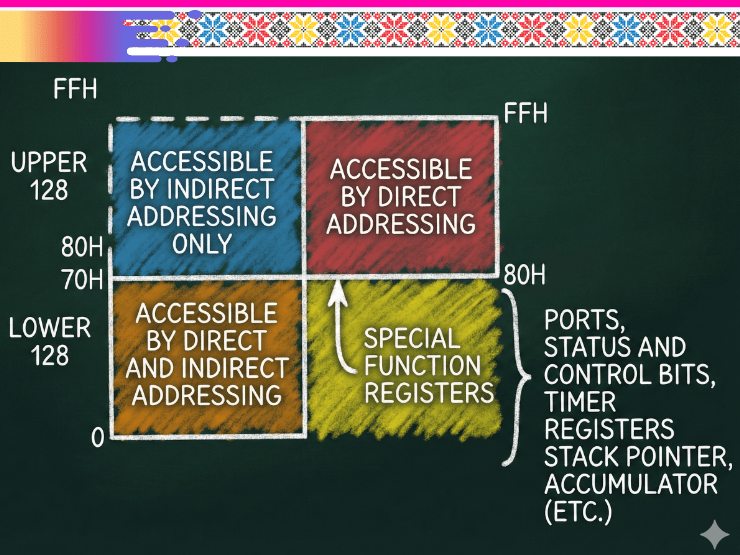

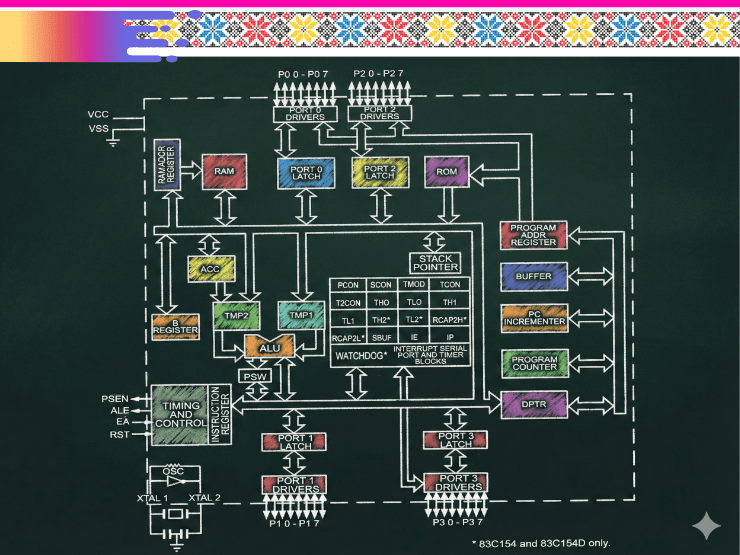

หน่วยความจำข้อมูลภายในของ MCS-51 มี 256 Byte แบ่งออกเป็นสองส่วนคือ ส่วนพื้นที่เฉพาะของ CPU ใช้งานเท่านั้น และพื้นที่ใช้งานทั่วไปสำหรับโปรแกรมใช้งานที่ผู้ใช้สร้างขึ้นมา

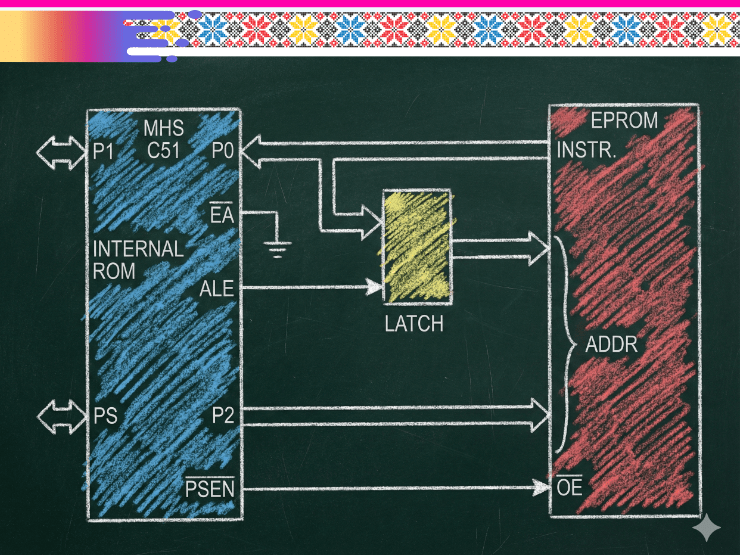

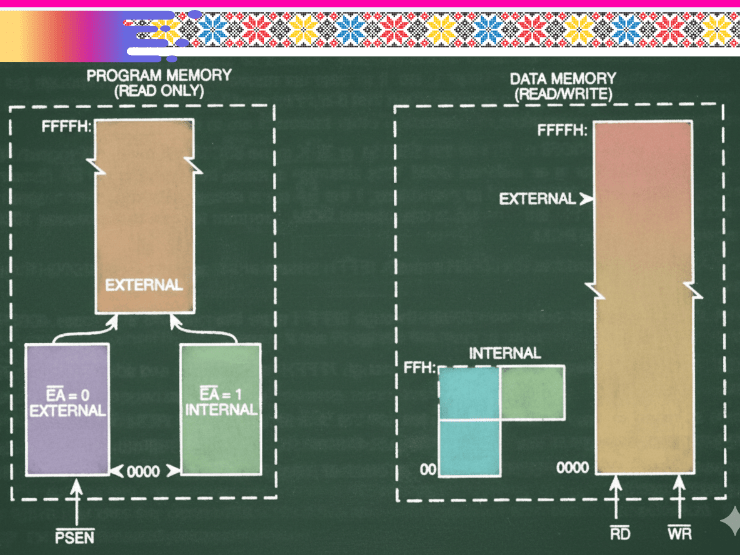

MCS-51 สามารถกับหน่วยความจำภายนอก EPROM เมื่อหน่วยความจำ ROM ที่มามาให้ภายในไม่เพียงพอ หรือเพื่อเป็นการทดลองงานต้นแบบ

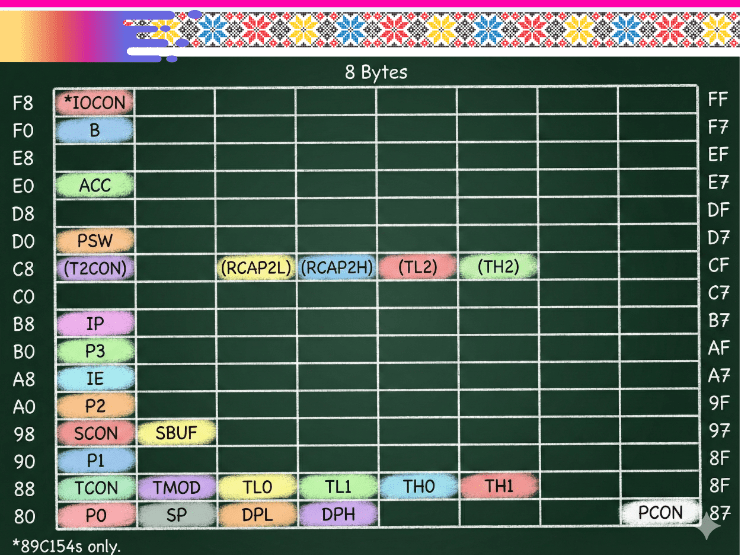

พื้นที่หน่วยความจำ SFR ตั้งแต่ Address 80h~FFh เป็นบริเวณของหน่วยความจำที่มีการใช้งานเฉพาะของ MSC-51 เท่านั้น โดยจะนำมาใช้เป็นตำแหน่งของ Special Function Register จำนวน 20 ตำแหน่ง

หน่วยความจำภายในตัวไมโครคอนโทรลเลอร์ MCS-51 มีมาให้ภายในแต่จำนวนมากน้อยขึ้นอยู่กับเบอร์ของ IC และหากต้องการหน่วยความจำมากกว่าที่มีมาให้ก็สาสมารถต่อเพิ่มภายนอกได้ด้วย

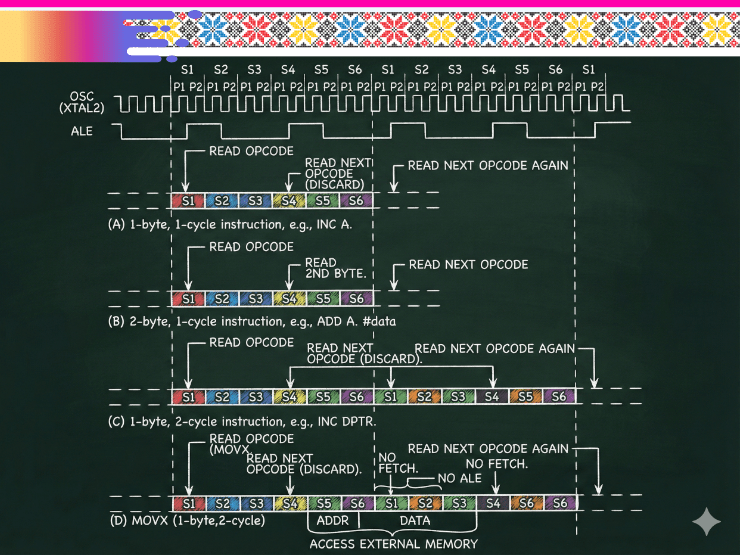

MCS-51 มีวงจรออสซิลเลเตอร์อยู่ภายในสำหรับสร้างพัลส์สัญญาณนาฬิกา ซึ่งจะนำไปเป็นฐานเวลาของหน่วยการทำงานทั้งหมดให้สอดคล้องกัน

MCU แตกต่างจาก CPU ตรงที่ตัว Microcontroller ได้รวมเอา ROM, RAM, Control port และอื่นๆ รวมเข้าด้วยกันทำให้มีขนาดที่เล็ก เหมาะกับการนำไปใช้ในวงจรควบคุมเครื่องใช้ไฟฟ้าต่างๆ

” Silence is the canvas of the creative mind. ”